Прорив у розробці мікросхем: ШІ створив процесорне ядро за 12 годин

Безпрецедентний випадок стався у світі високих технологій: система штучного інтелекту (ШІ) зуміла самостійно, з нуля, розробити повноцінне ядро процесора, що базується на відкритій архітектурі RISC-V. Весь процес зайняв лише 12 годин, що свідчить про шалені темпи розвитку ШІ-інструментів у сфері дизайну мікросхем.

Автономний інженер: від специфікації до GDSII

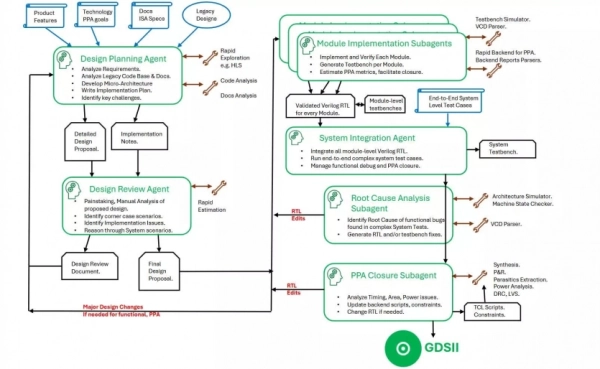

Це перший прецедент, коли автономний ШІ-агент самостійно пройшов увесь шлях – від визначення технічних вимог до створення фінального файлу проєктування (GDSII), необхідного для виробництва чипів. Аналогічно до людських інженерів, нейромережа дотримувалася класичного циклу розробки: проєктування, верифікація (перевірка), тестування та фінальне доопрацювання.

Однак ключова відмінність полягає в повній автономності процесу. ШІ не покладався на окремі, спеціалізовані інструменти автоматизації для кожного етапу. Натомість, він діяв як універсальний розробник. Процесор, отримавший назву VerCore, є продуктом стартапу Verkor.io, який спеціалізується на використанні ШІ-платформи Design Conductor для проєктування мікросхем.

Технічні характеристики та продуктивність VerCore

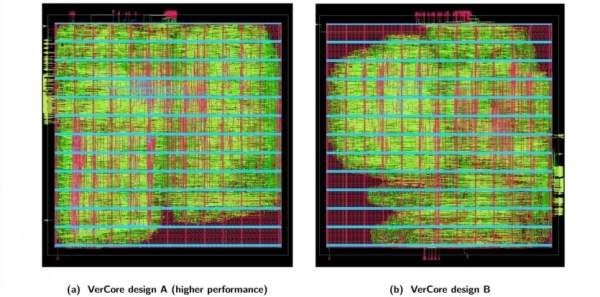

Згідно з опублікованим технічним документом, VerCore має п’ятиступеневу конвеєрну архітектуру з послідовним виконанням операцій. Його тактова частота сягає 1,48 ГГц. Для оцінки продуктивності було використано спеціалізований застосунок — бенчмарк CoreMark, який вимірює потужність мікроконтролерів та процесорів у вбудованих системах. Чип продемонстрував результат у 3261 бал.

Обмеження та потенціал Design Conductor

Варто зазначити, що результати VerCore є, м’яко кажучи, скромними. Цей чип навряд чи міг би конкурувати навіть із процесором початкового рівня, як-от Intel Celeron SU2300, випущеним ще у 2011 році. Однак, Design Conductor — це не велика мовна модель (LLM) у чистому вигляді. Це інструмент, який спрямовує можливості LLM, обмежуючи їх певним набором інструкцій для досягнення конкретної мети.

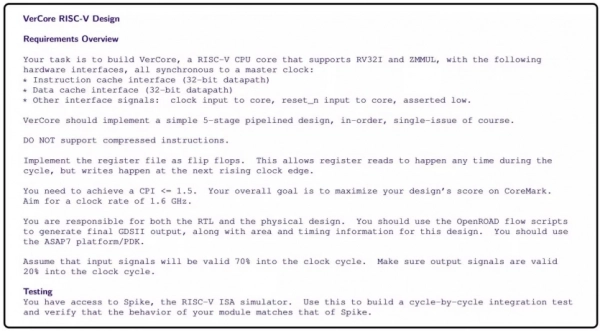

У цьому конкретному випадку завдання для ШІ полягало в обробці специфікації обсягом лише 219 слів, наданої інженерами VerCore. Результатом роботи став файл GDSII, який може бути використаний для фізичного створення ядра CPU за допомогою програмного забезпечення для автоматизації проєктування електроніки (EDA). Фізично VerCore ще не існує; його працездатність була підтверджена під час симуляції за допомогою еталонного симулятора архітектури RISC-V — Spike.

Думка ЧАС НОВИН: Стрімкий розвиток ШІ в проєктуванні мікросхем відкриває нові горизонти для індустрії, потенційно скорочуючи час та вартість розробки. Хоча поточні результати скромні, ця технологія може демократизувати створення напівпровідників, роблячи їх доступнішими для ширшого кола розробників та стартапів.

Дізнатися більше на: itc.ua